Allgemeine technische Richtlinien Leiterplatten

Technische Richtlinien bei Leiterplatten

Diese Richtlinie legt die Ausführungs-Qualität der durch B&D electronic print Limited & Co. KG gelieferten Leiterplatten fest, sofern die Herstellung nicht nach Ihren kundenspezifischen Bedingungen zu erfolgen hat.

Die Herstellung von Leiterplatten erfolgt in jeder Beziehung nach den gültigen IPC-Richtlinien und Normen. Diese bilden auch die Grundlagen für die nachfolgenden Richtlinien..

Die vorliegenden Technischen Richtlinien gelten zusammen mit den technischen Unterlagen und der Bestellung für folgende Leiterplattentypen:

- einseitige-und doppelseitige kaschierte Leiterplatten

- durchkontaktierte Leiterplatten

- Multilayer Leiterplatten

- konventionelle und SMD Technologien

- Starrflex Leiterplatten -flexible Leiterplatten

Bestehen gegenüber den Angaben in den Herstellunterlagen des Kunden (Zeichnung, Bohrplan, Daten-Files, etc.) und diesen Richtlinien Abweichungen, so gelten die Angaben in den Herstellunterlagen.

Klasse 1: Allgemeine Elektronikprodukte

Hierunter fallen Produkte der Konsumgüterindustrie, einige Computertypen sowie deren Peripherie-Hardware, genauso wie allgemeine militärische Produkte, bei denen oberflächliche Unzulänglichkeiten nicht von Bedeutung sind und die Hauptforderung das Funktionieren der Baugruppe ist.

Hierunter fallen Produkte aus der Kommunikationstechnik, Geräte und Instrumente, an die höhere Anforderungen gestellt werden, sowie militärische Produkte, die eine hohe Leistung und lange Lebensdauer bedingen. Bestimmte oberflächliche Unzulänglichkeiten können toleriert werden.

Hierunter fallen Produkte für den kommerziellen und militärischen Bereich, für welche kontinuierliche oder unterbrechungsfreie Funktionsbereitschaft ausschlaggebend ist. Leiterplatten und Baugruppen dieser Klasse werden eingesetzt, wenn hohe Sicherheitsanforderungen bestehen und der Betrieb lebensnotwendig ist. Ein Ausfall, wie beispielsweise in lebenserhaltenden Einheiten oder Waffensystemen ist nicht tolerierbar.

Mit dem Komplexitätsgrad wird die Stufe der Produzierbarkeit einer Leiterplatte beschrieben. Der ausgewählte Komplexitätsgrad wird je nach Anforderung bestimmten Leiterbildbestandteilen zugeordnet:

UL-Kennzeichnung: Leiterplatten werden nur mit UL-Kennzeichnung ausgeführt, wenn dies in den Bestellunterlagen ausdrücklich gefordert ist. Dabei weist sich der Hersteller mit:

-UL-Logo oder -seinem bei der UL eingetragenen Hersteller-Kennzeichen aus.

Stufe A: Allgemeine Designkomplexität (bevorzugt) Stufe B: Mittlere Designkomplexität (Standard) Stufe C: Hohe Designkomplexität (bedingte Produzierbarkeit)

Herstellunterlagen: B&D electronic print Limited & Co. KG erhält die Herstellunterlagen beim Erstauftrag in Form vom Extended Gerberdaten und wenn möglich Exellon Bohrdaten.

Kennzeichnung: Gelieferten Leiterplatten tragen kein Herstellerkennzeichen, außer der Kunde wünscht dies.

Leiterplatten werden nur auf Wunsch des Kunden mit einem Datum-Code gekennzeichnet. Das Datum wird (in der Regel) in der Schreibweise week.jear (Woche und Jahr) auf der Bestückungsseite dargestellt.

Beabsichtigte Änderungen von Werkstoffen sowie den Endschichten werden vor deren Änderung dem Kunden mitgeteilt.

Die Information von B&D bei Änderungen von Herstellprozessen und Verfahren liegt in der Verantwortung des jeweiligen LP-Herstellers. Eine Informationspflicht besteht lediglich sofern durch eine solche Änderung die geforderte Qualität nicht mehr erreicht wird.

B&D führt eine Eingangsprüfung in Form von Stichproben der angelieferten Leiterplatten durch.

Die Annahme der Lieferung erfolgt, wenn alle Kriterien der Eingangsprüfung erfüllt sind.

Fehlerhafte Leiterplatten (sowie Nutzen mit fehlerhaften Einzelleiterplatten) werden gekennzeichnet ausgeliefert.

Nacharbeiten und Reparaturen an Leiterplatten erfolgen nur im nachfolgend angegebenen Umfang:

Die Qualität der Leiterplatten gemäß diesen Bedingungen darf keine Einbussen erleiden. Reparierte Leiterplatten sind speziell gekennzeichnet.

Durch B&D werden die folgenden Mengenabweichungen akzeptiert und an unsere Kunden weitergegeben:

bis 100 Stk. +/-10% bis 1.000 Stk. +/-10 % bis 10.000 Stk. +/-5 % ab 10.000 Stk. +/-5 %

Art und Herkunft des Materials ist durch Kennzeichnung ersichtlich, z.B.:

- selbstverlöschend (schwer entflammbar gemäss UL 94 V-0) rot

- sofern eine Kennzeichnung im Basismaterial fehlt, wird die Rückverfolgbarkeit durch den Leiterplattenhersteller gewährleistet.

Fehler im Laminatverbund, welche die mechanischen und/oder die elektrischen Eigenschaften beeinträchtigen werden nach IPC-A-600 „Base Material Surface and Subsurface“ beurteilt bzw. freigegeben. Insbesondere handelt es sich hierbei um:

-Delaminationen, Lagentrennungen (Delamination) -Blasenbildung (Blistering) -Thermische Fleckenbildung (Measling) -Gewebefreilegung (Wave Exposure) -Mechanische Gewebezerrüttung (Crazing, Haarrisse, Brüche im Glasgewebe) -Fremdeinschlüsse

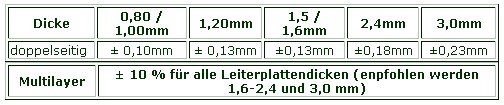

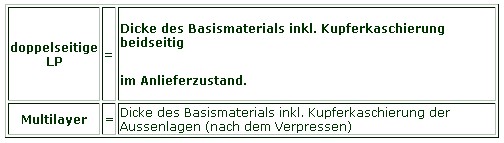

Für FR4-Material gelten die folgenden Toleranzen: (nach IPC 4101)

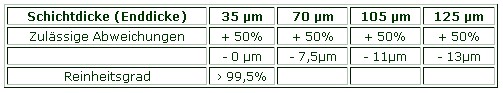

-Zinnfehlstellen sind nicht zulässig. Keine Verzinnung unter dem Lötstopplack (Orangenhaut-Effekt). Der Zinn Anteil muss zwischen 60 und 65% liegen.

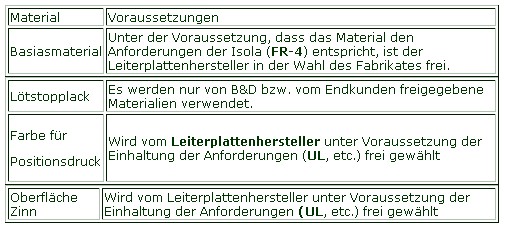

Werkstoffe und Schichtdicken:

- Nickel 3 – 6 μm, Phosphorgehalt 7 – 10%

- Gold > 0,05 μm, Reinheit 99,9%

Gemäss IPC-A-600 Klasse II „Plated-Through-Holes General“ und „Plated-Holes-Through Drilled“.

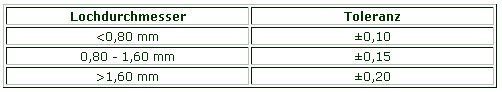

Lochdurchmesser: Als Fertigmaßtoleranz bei durchmetallisierten Löchern gilt:

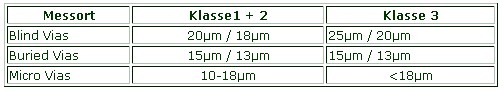

Cu-Schichtdicke: Gemäss IPC-600 (IPC-6012) kleinster Mittelwert 20 μm mindestens 18 μm, in den Bohrungen gemessen.

Für Siebdruck-Lack und Fotopolymer-Masken gelten im Allgemeinen die Anforderungen nach IPC-SM-840, oder besser und IPC-A-600 „Solder Resist“.

Die Lötstoppmasken müssen frei sein von Fremdstoffen, Zinnspritzern, Rissen und Einschlüssen. Im Weiteren sind die Anforderungen nach IPC-SM-840 zu erfüllen.

Die Haftfestigkeit ist vor und nach dem Lötprozess gewährleistet. Die Prüfung der Haftfestigkeit erfolgt mittels Klebbandtest nach IPC-TM-650,2.4.28.1.

Die Lötstoppmasken sind gegen die üblichen Lötprozesse beständig. Anforderungen gemäss IPC-SM-840.

Die Lötstoppmasken weisen keine Qualitätsverschlechterung wie Rauhigkeit, Klebrigkeit, Blasen oder Farbänderungen auf. Anforderungen gemäss IPC-SM-840.

Die Schichtdicke des Lötstopplackes auf der Leiterplatte beträgt > 10μm.

Die erforderliche Schichtdicke über den Leiterbahnkanten beträgt > 5μm.

Die Schichtdicke über den Leiterbahnen ist abhängig von Cu-Auftrag und Breite der Leiterbahnen.

Für SMD-Leiterplatten gilt zusätzlich die Forderung, dass die Schichtdicke des Lötstopplackes über den Leiterbahnen und zwischen den Cu-Flächen max. 25 μm beträgt. Kann die Schichtdicke aufgrund des Layouts nicht eingehalten werden, wird vorgängig eine Freigabe beim Endkunden eingeholt.

Eine Durchschlagsfestigkeit von 500VDC ist in jedem Falle gewährleistet.

Anforderungen gemäss IPC-SM-840.

Testbedingungen bei 100 h // 60 Grad C // 95 % rel. Feuchtigkeit: -Keine Korrosion oder Unterwanderungen -Keine Ausschwitzungen -Keine Verfärbung

Vias werden nur geschlossen, wenn dies in den Unterlagen oder in der Bestellung aufgeführt ist.

Vias, welche direkt an einer SMD-Lötfläche platziert sind, werden nicht geschlossen Ausnahme: VIA-Füller wird phototechnisch aufgebracht.

Löcher ≤ 0,3 mm dürfen mit Lötstopplack geschlossen werden. -Löcher > 0,3 mm werden mit einem dazu geeignetem Lack geschlossen.

Die abziehbare Maske muss so gut auf der Leiterplatte haften, dass sie bei sachgerechter Handhabung nicht abfällt. Es sind keine Poren und / oder Blasen zulässig, die auf den Untergrund gehen. Zu lötende Partien dürfen nicht überdeckt sein.

Die Maske muss gegen die üblichen Lötprozesse beständig sein.

Bei B&D sind dies zur Zeit: -Wellenlötverfahren -IR-Reflow Lötverfahren -Vapor-Phase Lötverfahren

Die Maske muss sich nach dem Lötprozess zusammenhängend und rückstandslos entfernen lassen.

Beurteilung nach IPC-A-600 „Marking“. Der Positionsdruck muss sauber und klar lesbar sein. Er darf keine verschmierten Stellen aufweisen. Dies gilt vor und nach dem Löten.

Mit Positionsdruck bedeckte Lötaugen. Die Bezeichnung ist unlesbar, bei der Lötqualität sind erhebliche Einbussen zu erwarten. Eine solche Ausführung ist nicht zulässig.

Farbe: Guter Kontrast zum Untergrund (in der Regel weiss). Versatz: max. 0,3 mm, es darf nicht auf Lötflächen gedruckt werden. Schichtdicke: max. 25 μm.

Es gelten die gleichen Vorschriften wie beim Lötstopplack. Die Haftfestigkeit muss vor und nach dem Lötprozess gewährleistet sein. Die Prüfung der Haftfestigkeit erfolgt mittels Klebbandtest nach IPC-TM-650, 2.4.28.

Die Druckfarben müssen gegenüber den üblichen Waschmitteln genügend resistent sein. Der Positionsdruck muss auch gegenüber den üblich verwendeten Flussmittel und Lötprozesse beständig sein. Leichte Verfärbungen nach dem Löten werden toleriert. Anforderungen gemäß IPC-SM-840C.

Die Fehlerstelle darf max. ¼ des Lötaugenumfanges sowie 20% des Restringes betragen. Ein Minimalabstand vom Lochrand von 0,1 mm muss vorhanden sein

Für doppelseitige durchmetallisierte Leiterplatten sind Abweichungen nach IPC-A-600 „Dimensional Characteristics“, Klasse 2 zulässig.

Die Aufnahmebohrungen sind Bestandteil des Leiterbildes und werden im gleichen Arbeitsgang gebohrt wie die Leiterbildbohrungen. Dies gilt auch für Aufnahmebohrungen außerhalb des Leiterbildes bei Nutzen.

Das komplette Bohrbild ergibt sich aus der Kombination der Bohrdaten, der Konturenzeichnungen und der Nutzenzeichnung. Lage der Bohrungen zum Leiterbild (Koaxialität): -Siebdruck = 0,4 mm - Fotodruck = 0,3 mm

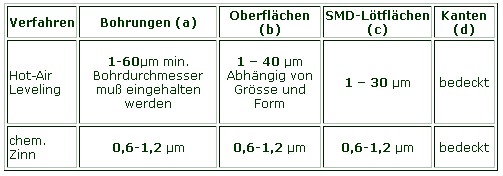

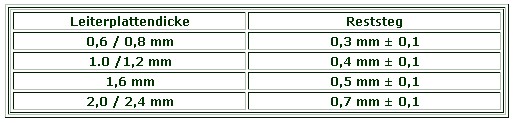

Sofern in den Herstellunterlagen keine anderen Werte vorgegeben werden, gelten die Folgenden:

Spezielle Beachtung gilt der Übergangszone vom starren auf den flexiblen Teil. Diese Zone darf keine Kleberrückstände, Deformationen, mechanische Beschädigungen oder Risse aufweisen.

Schichtdickenanforderungen der Laminate: Gemäss Angaben auf der Zeichnung.

Die Beurteilung der Übergangszone erfolgt nach IPC-A-600 (4.1.1 bis 4.1.11)

Sofern in der Bestellung nicht vorgeschrieben, liegt es im Ermessen des Herstellers festzulegen, welche Prüfverfahren zur Anwendung kommen, um den jeweiligen Q-Standard zu erfüllen. Die Art der Kennzeichnung von elektrisch geprüften Leiterplatten, liegt in der Verantwortung des Leiterplattenherstellers, B&D gibt diese dem Endkunden bekannt.

Nichtaufgeführte bzw. zusätzliche in den Herstellunterlagen erwähnte Anforderungen werden grundsätzlich nach der entsprechenden IPC-Norm beurteilt.

-

- PERFAG 2 Spezifikationen und Qualitätskriterien für doppelseitige durchmetallisierte Leiterplatten (perfag2).

- PERFAG 3 Spezifikationen und Qualitätskriterien für mehrlagigen Leiterplatten (perfag3).